- 超能网 >>

- 搜索

-

PCIe 6.0/7.0规范推进放缓,新技术的采用或面临延迟

吕嘉俭 发布于2024-06-15 11:16 / 关键字: PCIe 7.0, PCIe 6.0, PCI Express

近日,负责制定PCI Express规范的组织PCI-SIG举行了2024年开发者大会,提供了PCIe 6.0和PCIe 7.0的最新进展,并指出虽然正在不断推进规范制定的相关工作,但比最初预期的要慢,因此新技术的采用可能会面临一些延迟。

展开阅读

| 收藏 | 评论(1)

-

PCI-SIG发布CopprLink线缆规范:适用于PCIe 5.0和6.0标准

吕嘉俭 发布于2024-05-03 23:42 / 关键字: PCIe 6.0, PCI Express

展开阅读

| 收藏 | 评论

-

PCI-SIG确认PCIe 5.0/6.0将使用新线缆设计,名为“CopprLink”

吕嘉俭 发布于2023-11-15 17:43 / 关键字: PCIe 6.0, PCI Express

近日PCI-SIG在美国丹佛科罗拉多会议中心举行了SC23会议,向成员展示了PCIe技术演示和新的PCI快速线缆命名方案,强调了PCIe技术是高性能计算互连的首选。PCI-SIG表示,PCIe内部和外部线缆新命名方案为“CopprLink”,目前正在制定PCIe 5.0和PCIe 6.0的内部和外部线缆规范,目标是今年内发布。

PCI-SIG的演示重点是高性能计算(HPC),因此CopprLink可能会将目标放在了接口的数据传输上,以便为下一代平台上的各种设备提供最佳的传输带宽,供电问题或许不是考虑的重点。如果CopprLink与供电密切相关,那么应该会努力解决当前12VHPWR标准遇到的一些问题。虽然“12V-2×6 PCIe 6.0”连接器新设计已经发布了,不过似乎还有改进的余地。

展开阅读

| 收藏 | 评论(1)

-

Rambus推出PCIe 6.0接口子系统,面向下一代高性能数据中心和AI SoC解决方案

吕嘉俭 发布于2022-10-25 16:13 / 关键字: PCIe 6.0, PCI Express, Rambus

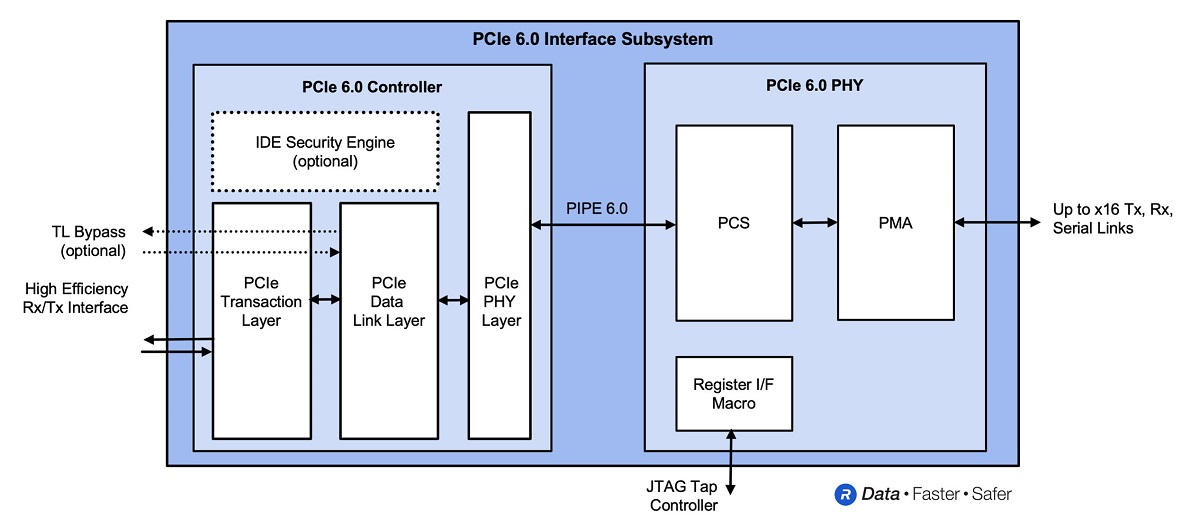

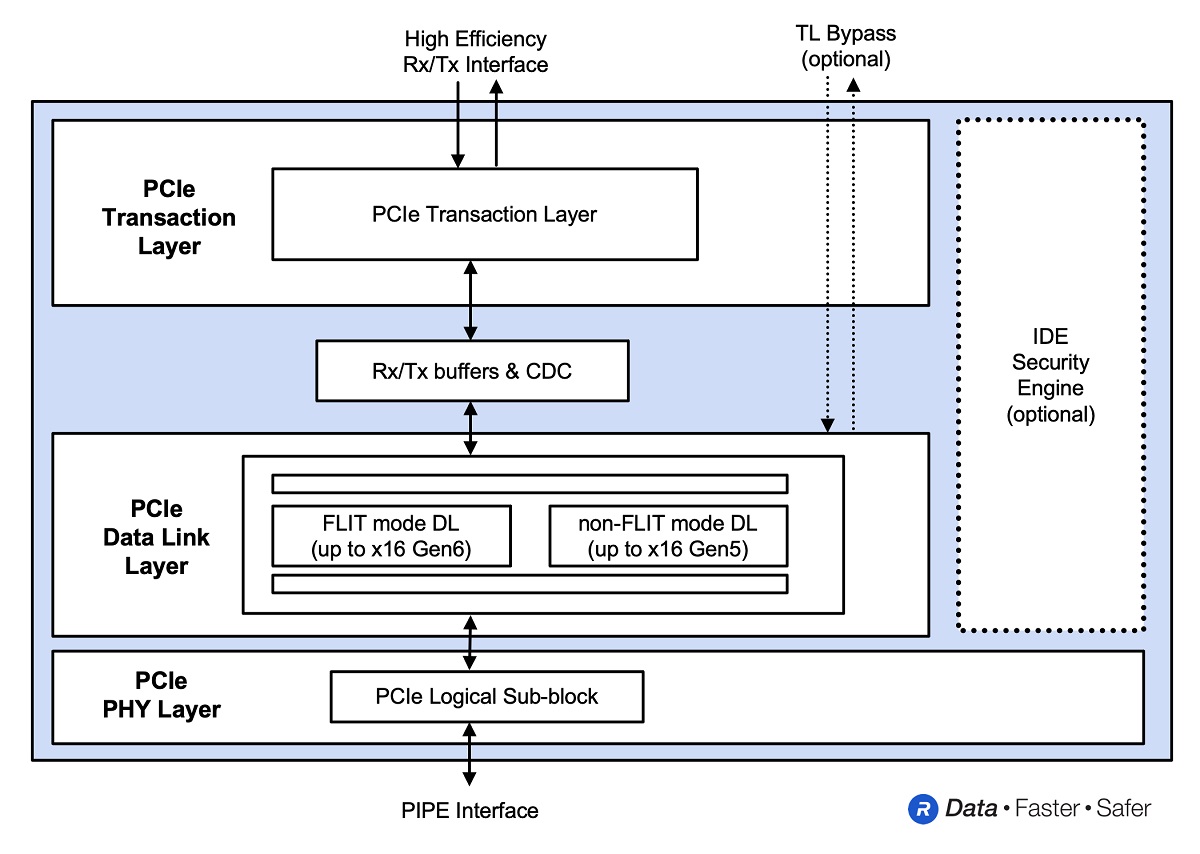

Rambus宣布,推出PCI Express(PCIe 6.0)接口子系统,由PHY和控制器IP组成,同时还支持最新的Compute EXpress Link(CXL)3.0规范,旨在为下一代高性能数据中心和AI SoC解决方案提供支持。

展开阅读

| 收藏 | 评论(3)

-

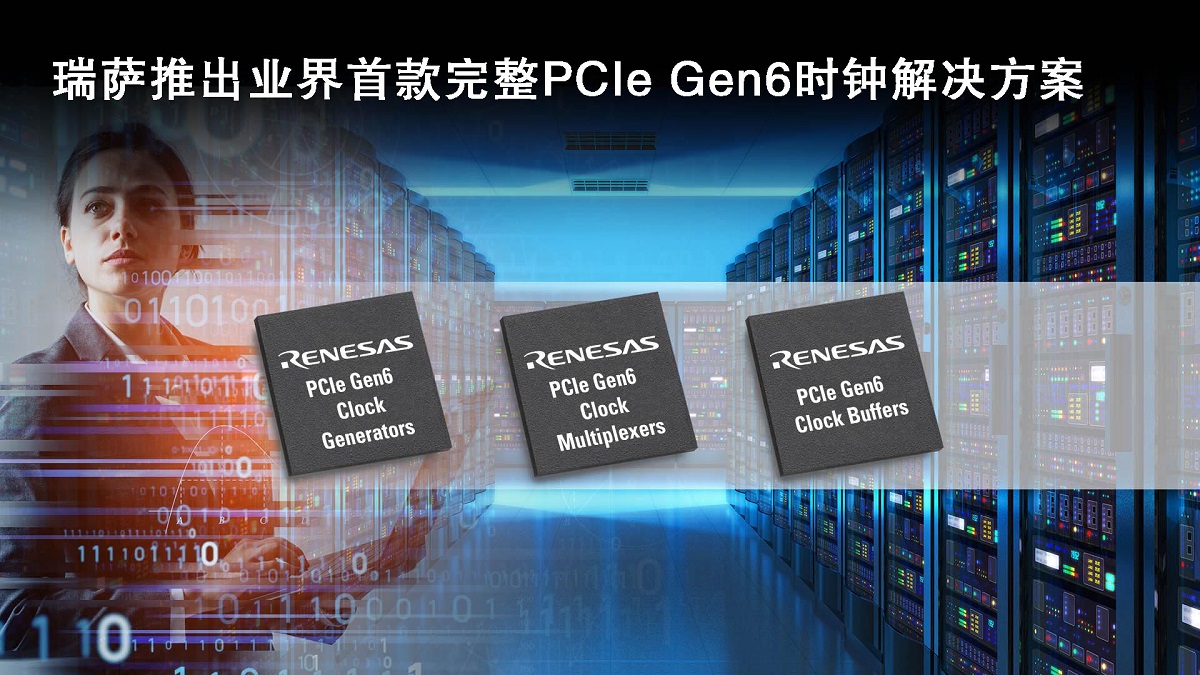

瑞萨电子发布PCIe 6.0时钟解决方案:多路输出、小尺寸封装、面向未来需求

吕嘉俭 发布于2022-04-15 11:00 / 关键字: 萨瑞电子, PCIe 6.0

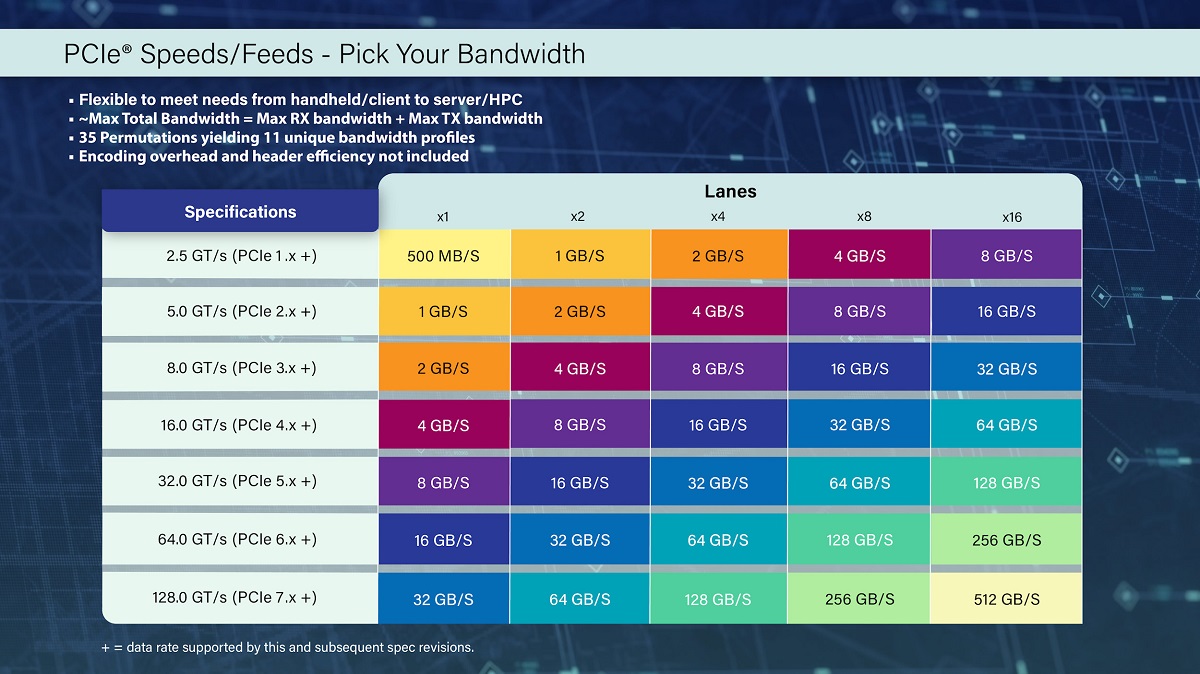

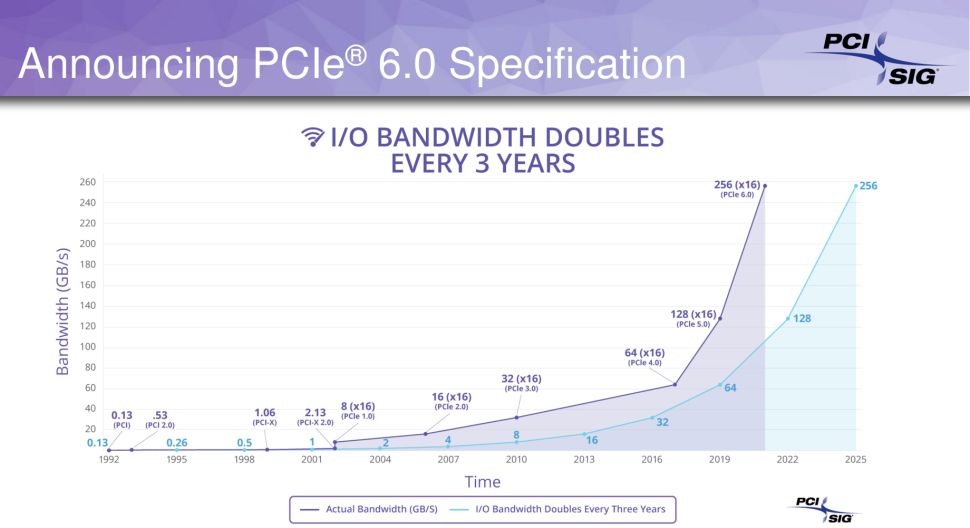

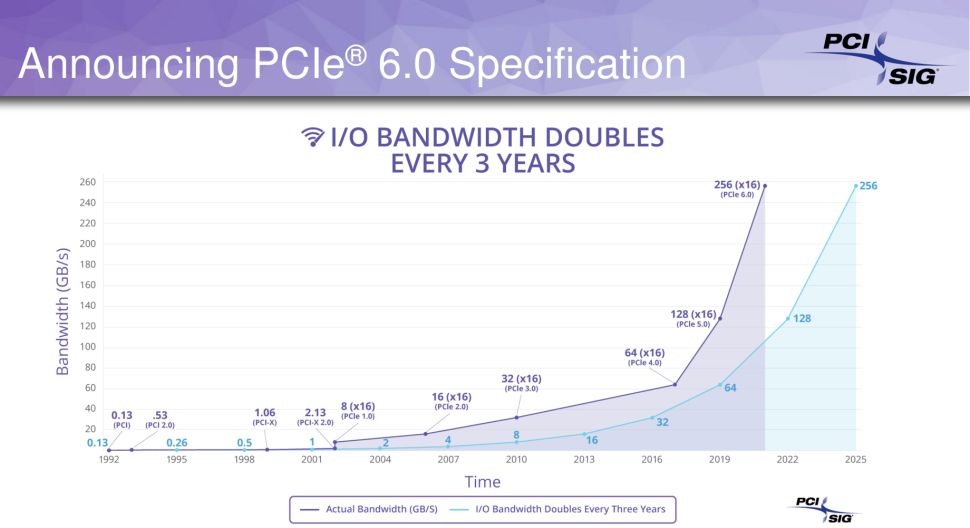

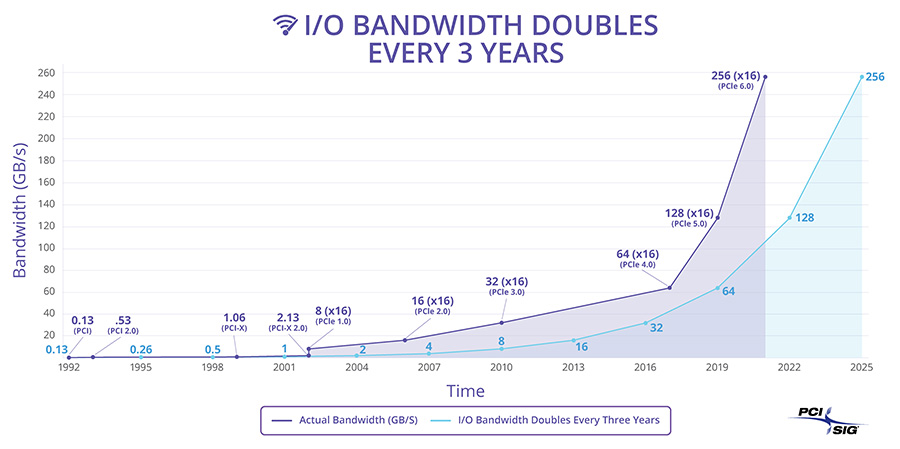

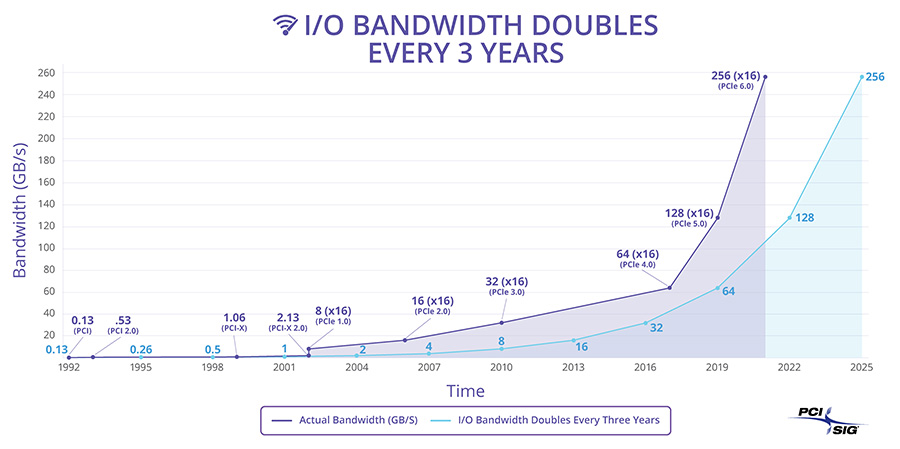

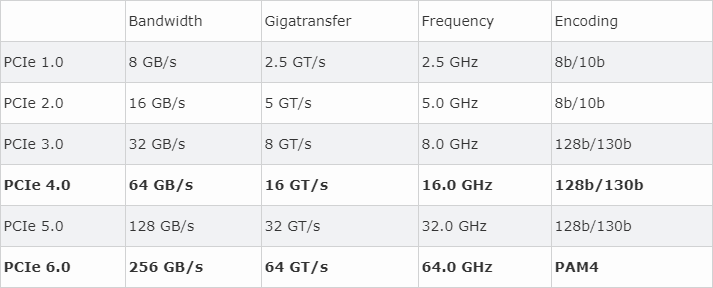

PCI-SIG在2022年1月,正式向其成员发布PCIe 6.0规范,同时也兑现了其承诺,即每发布一个PCIe新规范就会让带宽翻倍。PCI-SIG从2019年6月开始了PCIe 6.0规范的相关制定工作,前后经历了两年零七个月的时间,与PCIe 5.0规范的发布相隔不到三年。随着PCIe 6.0规范的发布,相关厂商也在产品上开始跟进。

展开阅读

| 收藏 | 评论(2)

-

Rambus发布PCIe 6.0控制器:为下一代数据中心提供64 GT/s的传输速率

吕嘉俭 发布于2022-01-28 10:52 / 关键字: PCIe 6.0, PCI Express, Rambus

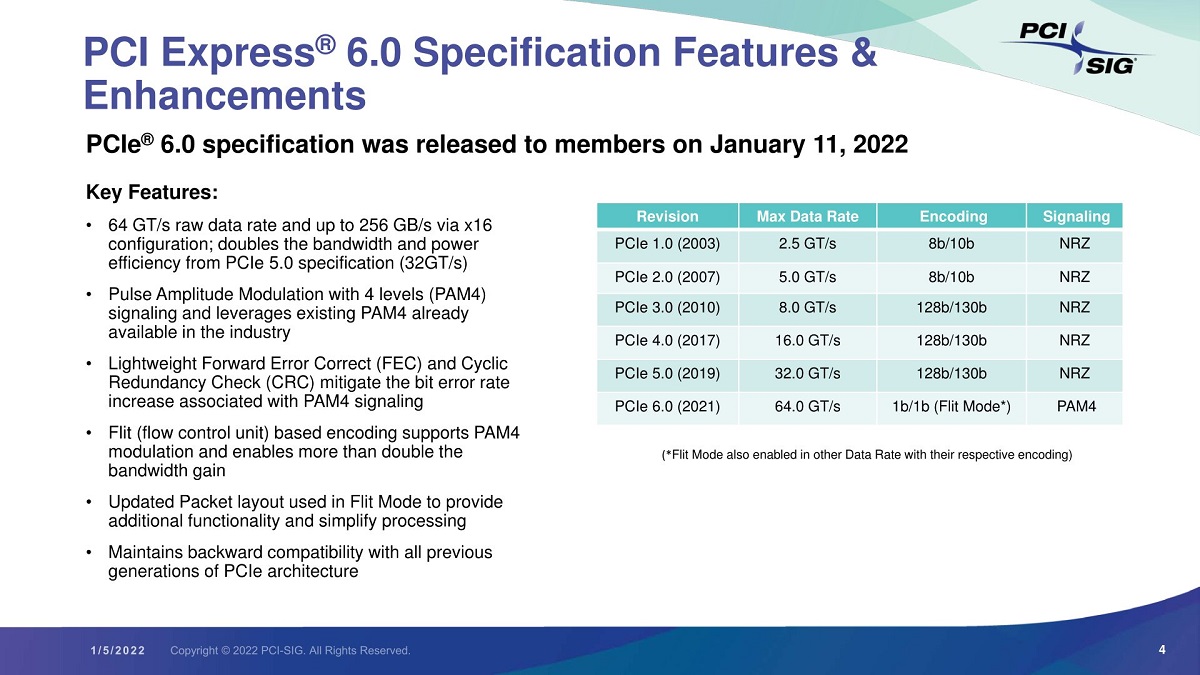

PCI-SIG在2022年1月正式向其成员发布了PCIe 6.0规范,PCIe新规范让带宽再次翻倍。PCI-SIG表示,PCIe 6.0规范的发布将有利于数据密集型市场,比如高性能计算(HPC)、数据中心、边缘计算、人工智能和机器学习(AI/ML)、汽车、物联网(IoT)以及航空航天等,并进一步加强了PCI Express作为高速互联的接口。

展开阅读

| 收藏 | 评论(2)

-

PCI-SIG正式发布PCIe 6.0规范,将有利于数据密集型市场

吕嘉俭 发布于2022-01-12 12:01 / 关键字: PCIe 6.0, PCI Express

PCI-SIG在2019年6月开始PCIe 6.0规范的相关制定工作,在经历了两年零七个月后,PCI-SIG在2022年1月正式向其成员发布PCIe 6.0规范。新规范是在PCIe 5.0规范发布不到三年后推出的,同时也兑现了PCI-SIG的承诺,即每发布一个PCIe新规范就会让带宽翻倍。

详细阅读

| 收藏 | 评论(5)

-

Cadence发布PCIe 6.0 IP测试芯片设计套件,采用台积电5nm工艺制造

吕嘉俭 发布于2021-11-05 15:55 / 关键字: Cadence, TSMC, 台积电, PCIe 6.0, PCI Express

大概在一个月前,PCI-SIG宣布PCIe 6.0已经到了0.9版本,相当于最终草案阶段。目前PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。除非出现重大问题,否则不允许进行任何功能上的修改,相关企业也可以开始在产品中采用PCIe 6.0。

展开阅读

| 收藏 | 评论(1)

-

PCIe 6.0规范进入最终草案阶段:×16通道单向速度达128 GB/s

吕嘉俭 发布于2021-10-08 14:22 / 关键字: PCIe 6.0, PCI Express

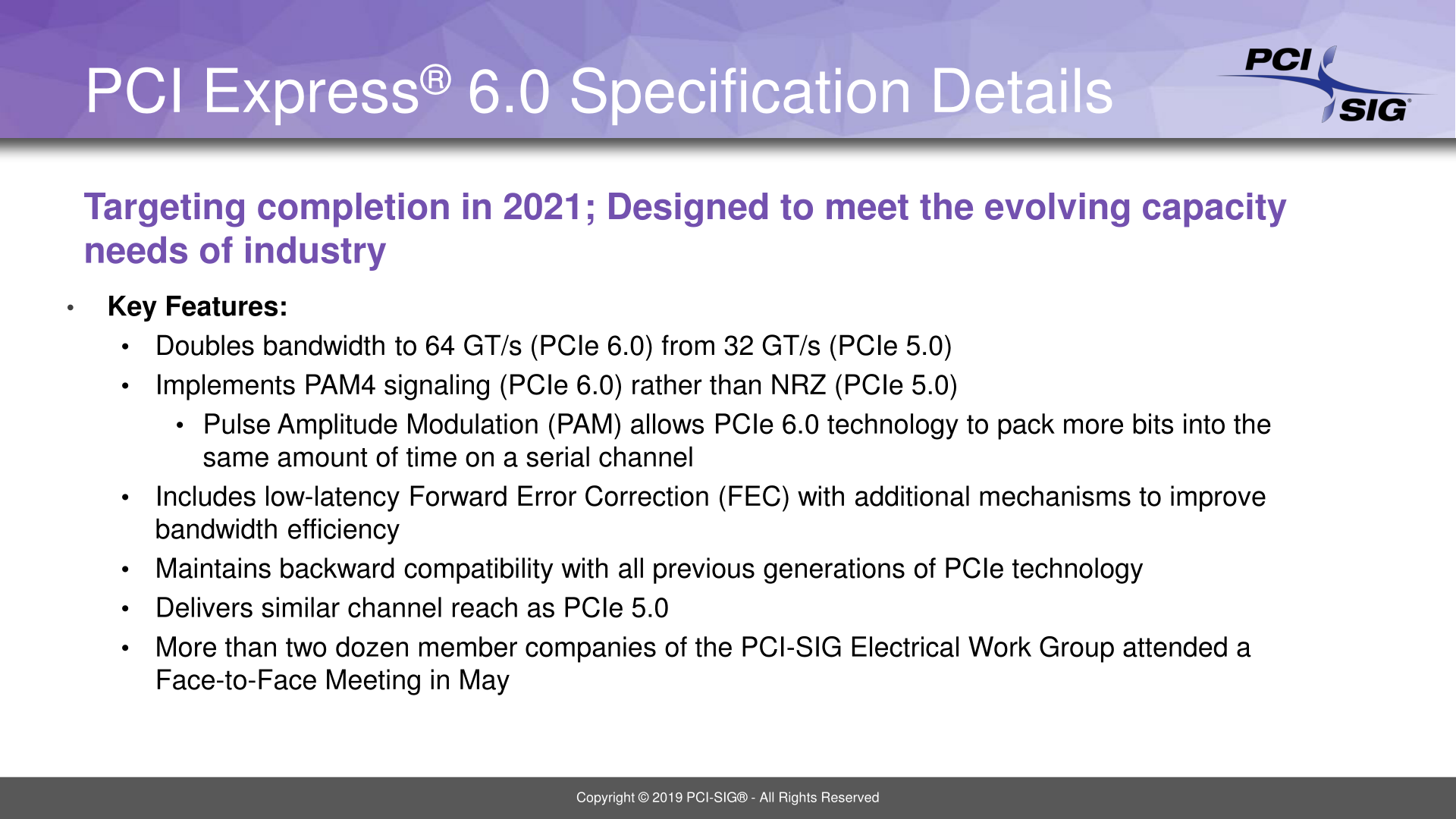

PCI-SIG在2019年6月开始PCIe 6.0相关工作,在经历了两年零四个月后,目前PCIe 6.0已经到了0.9版本,相当于最终草案阶段。PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。除非出现重大问题,否则不允许进行任何功能上的修改。这意味着相关的公司可以开始在产品中采用PCIe 6.0,以确保产品符合规范草案。

展开阅读

| 收藏 | 评论(3)

-

Synopsys推出业界首个PCIe 6.0的完整IP解决方案,不过离消费市场还比较遥远

吕嘉俭 发布于2021-03-22 18:16 / 关键字: Synopsys, PCIe 6.0

新思科技(Synopsys)宣布推出业界第一个针对PCI Express(PCIe)6.0技术的完整IP解决方案,其中包括控制器(具有Synopsys接口或可选ARM的AMBA 5/4/3 AXI接口)、PHY和验证IP,可实现PCIe 6.0片上系统(SoC)设计的早期开发。新的PCIe 6.0 DesignWare IP支持标准规范中的最新功能,包括64 GT/s PAM-4信号,FLIT模式和L0p功耗状态。

展开阅读

| 收藏 | 评论(4)

-

PCIe 6.0规范走到里程碑:完整的协议草案已经准备就绪

吕嘉俭 发布于2020-11-05 11:22 / 关键字: PCIe 6.0, PCI Express

PCIe 6.0规范在本周取得了一个重要的阶段性胜利,PCI-SIG向其成员发布了0.7版本规格。

这表明,该技术规格已经被基本确定,其电气规格已经通过测试芯片验证,意味着PCIe 6.0已经准备好了,并且可以正常使用,所以在2021年的某个时候,64 GT/s的PCIe 6.0和PAM4编码最终确定只是时间问题。

详细阅读

| 收藏 | 评论(11)

-

PCI-SIG组织发布PCIe 6.0规范的0.5版本:正式标准预计将于2021年登场

倪嘉声 发布于2020-02-22 09:53 / 关键字: PCI-SIG, PCIe 6.0

PCI-SIG组织于本周向其成员发布了PCIe 6.0规范最新的0.5号版本,该版本是PCIe 6.0规范的第一份草案,主要完成了0.3版本中提出的PCIe 6.0主要特性。

展开阅读

| 收藏 | 评论(10)

-

PCI-SIG组织推出PCIe 6.0规范:采用PAM4编码,带宽达到256GB/s

王智勇 发布于2019-06-19 09:58 / 关键字: PCI-SIG, PCIe 6.0, PAM4

我们目前还不清楚将要在下个月随着AMD Ryzen 3000系列处理器一同走向大众领域的PCIe 4.0会对我们的日常应用带来多大的提升,更不要说此前刚刚完成的PCIe 5.0。但是显然PCI-SIG并不满足于当前的技术,于是推出了PCIe 6.0。

展开阅读

| 收藏 | 评论(23)

图片来源:Tom's Hardware

图片来源:Tom's Hardware