- 超能网 >>

- 搜索

-

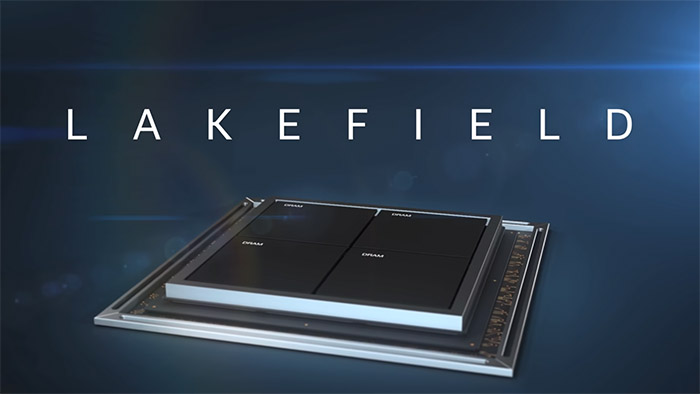

英特尔公布Lakefield细节:3D多层堆叠+大小核搭配、超小封装实现完整计算SoC

唐裕之 发布于2019-08-21 17:12 / 关键字: 英特尔, Lakefield, 3D堆叠, Sunny Cove

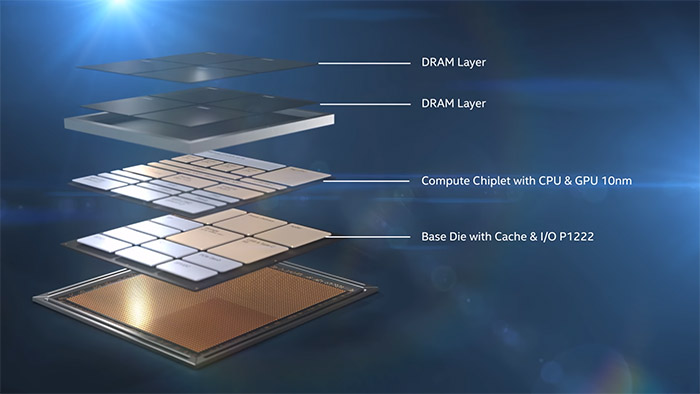

英特尔早在几个月前就确认了Lakefield处理器,这款处理器最重要的技术就是英特尔的Foeveros 3D封装技术,可以将不同架构、工艺的核心封装在一起,提供了极大地灵活性。在近日的Hot Chips 31会议中,英特尔也将一些技术细节公布出来。

详细阅读

| 收藏 | 评论(13)

-

利用半导体制冷,AMD新专利有望解决3D堆叠散热问题

Strike 发布于2019-07-01 10:00 / 关键字: AMD, 3D堆叠, 半导体散热

随着半导体制程工艺的升级难度越来越大,进度越来越缓慢,台积电的7nm工艺开发成本已经超过了30亿美元,接下来的5nm工艺预计要超过50亿美元,在平面上想提升晶体管密度这事情已经变得相当有挑战性,3D度堆叠工艺可能是解决这问题的一个好方法,结构简单的NAND闪存已经大面积转向3D堆叠工艺了,HBM显存也是利用3D堆叠工艺生产的,但是3D堆叠工艺也不是万能的,散热就是3D堆叠工艺要面临的一大难题,层数越多热量堆积就越严重,AMD近日申请的一项专利就有可能解决这一问题的。

CPU也要上3D堆叠工艺了,这是Intel采用Foveros 3D封装工艺所生产的Lakefield SoC

CPU也要上3D堆叠工艺了,这是Intel采用Foveros 3D封装工艺所生产的Lakefield SoC详细阅读

| 收藏 | 评论(8)

-

不遑多让,AMD有望将3D堆叠SRAM和DRAM用于其CPU和GPU

杨申圳 发布于2019-03-18 10:42 / 关键字: AMD, CPU, GPU, 摩尔定律, 3D堆叠

Intel在去年12月的“架构日”活动上公布了名为“Foveros”的全新3D封装技术,该技术首次引入了3D堆叠的优势,可实现在逻辑芯片上堆叠逻辑芯片,当时Intel展出使用该技术制造的Hybrid x86 CPU,也公布了一些规格细节。老对手AMD当然也不甘落后,AMD在最近的活动中透露,他们正致力于在其处理器之上使用3D堆叠DRAM和SRAM的新设计来提高性能。

详细阅读

| 收藏 | 评论(7)

-

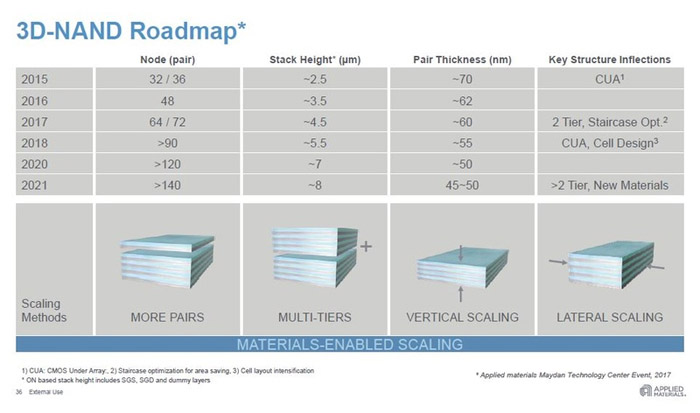

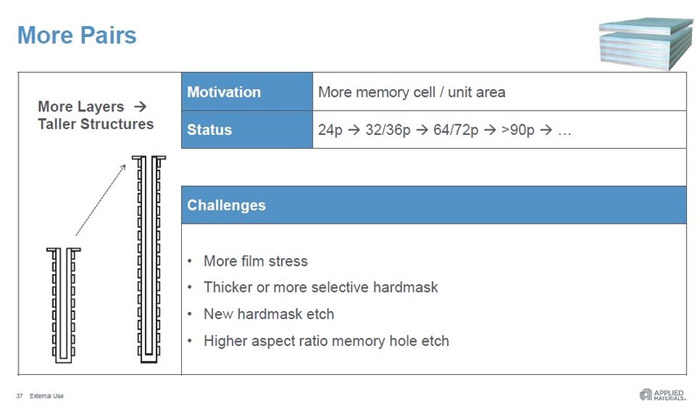

3D NAND未来线路图,到了2021年我们将用上140层堆叠的闪存

Strike 发布于2018-05-15 09:56 / 关键字: 3D NAND, 3D堆叠, 3D闪存

在正在举行的国际存储研讨会2018(IMW 2018)上,应用材料公司Sean Kang介绍了未来几年3D-NAND的发展线路图,到了2021年,3D-NAND的堆叠层数会超过140层,而且每一层的厚度会不断的变薄。

展开阅读

| 收藏 | 评论(4)

-

谋划内存技术未来,微软加入HMC阵营

bolvar 发布于2012-05-09 09:37 / 关键字: 微软, HMC, 3D堆叠

据报道,微软近日宣布加入HMC组织,该组织是由美光、三星、IBM、Open-Silicon以及Xilinx组成,目的是制定与现有RAM内存标准兼容的HMC内存标准。

HMC(Hybrid Memory Cube,混合内存魔方)被视为RAM技术的未来,与现有技术相比,其带宽有极大增长,内存延迟大幅降低,而功耗更低。简单来说,HMC内存也是一种芯片3D堆叠技术,多层RAM电路可以层叠在一起,内存性能是现有标准的20倍,而功耗只有后者十分之一。

展开阅读

| 收藏 | 评论(1)

HMC内存想象图,立体堆叠设计看起来真的很像魔方

HMC内存想象图,立体堆叠设计看起来真的很像魔方